Processeur - Définition

La liste des auteurs de cet article est disponible ici.

Conception et implémentation

Le codage des nombres

La manière dont un CPU représente les nombres est un choix de conception qui affecte de façon profonde son fonctionnement de base. Certains des ordinateurs les plus anciens utilisaient un modèle électrique du système numérique décimal (base 10). Certains autres ont fait le choix de systèmes numériques plus exotiques comme les systèmes trinaires (base 3). Les processeurs modernes représentent les nombres dans le système binaire (base 2) dans lequel chacun des chiffres est représenté par une grandeur physique qui ne peut prendre que 2 valeurs comme une tension électrique "haute" ou "basse".

Le concept physique de tension électrique est analogique par nature car elle peut prendre une infinité de valeurs. Pour les besoins de représentation physique des nombres binaires, les valeurs des tensions électriques sont définies comme des états 1 et 0. Ces états résultent des paramètres opérationnels des éléments de commutation qui composent le processeur comme les niveaux de seuil des transistors.

En plus du système de représentation des nombres, il faut s'intéresser à la taille et la précision des nombres qu'un processeur peut manipuler. Dans le cas d'un processeur binaire, un "bit" correspond à une position particulière dans les nombres que le processeur peut gérer. Le nombre de bits (chiffres) qu'un processeur utilise pour représenter un nombre est souvent appelé "taille du mot" (word size, bit width, data path width) ou "précision entière" lorsqu'il s'agit de nombres entiers (à l'opposé des nombres flottants). Ce nombre diffère suivant les architectures, et souvent, suivant les différents modules d'un même processeur. Par exemple, un CPU 8-bit gère des nombres qui peuvent être représentés par 8 chiffres binaires (chaque chiffre pouvant prendre 2 valeurs), soit 28 ou 256 valeurs discrètes. En conséquence, la taille du nombre entier défini une limite à la plage des nombres entiers que le logiciel exécuté par le processeur pourra utiliser.

La taille du nombre entier affecte également le nombre d'emplacements mémoire que le processeur peut adresser (localiser). Par exemple, si un processeur binaire utilise 32 bits pour représenter une adresse mémoire et que chaque adresse mémoire est représentée par un octet (8 bits), la taille mémoire maximum qui peut être adressée par ce processeur est de 232 octets, ou 4 Go. C'est une vision très simpliste de l'espace d'adressage d'un processeur et beaucoup de conceptions utilisent des types d'adressages bien plus complexes, comme la pagination, pour adresser plus de mémoire que la taille du nombre entier le leur permettrait avec un espace d'adressage à plat.

De plus grandes plages de nombres entiers nécessitent plus de structures élémentaires pour gérer les chiffres additionnels, conduisant à plus de complexité, des dimensions plus importantes, plus de consommation d'énergie et des coûts plus élevés. Il n'est donc pas rare de rencontrer des microcontrôleurs 4-bit ou 8-bit dans des applications modernes, même si des processeurs 16-bit, 32-bit, 64-bit et même 128-bit sont disponibles. Pour bénéficier des avantages à la fois des tailles d'entier courtes et longues, beaucoup de CPU sont conçus avec différentes largeurs d'entiers dans différentes parties du composant. Par exemple, le System/370 d'IBM est doté d'un CPU nativement 32-bit mais qui utilise une unité de calcul flottant (FPU) de 128-bit de précision pour atteindre une plus grande précision dans les calculs avec les nombres flottants. Beaucoup des processeurs les plus récents utilisent une combinaison comparable de taille de nombres, spécialement lorsque le processeur est dédié à un usage généraliste pour lequel il est nécessaire de trouver le juste équilibre entre les capacités à traiter les nombres entiers et les nombres flottants.

Le signal d'horloge

La plupart des processeurs, et plus largement la plupart des circuits de logique séquentielle, ont un fonctionnement synchrone par nature. Cela veut dire qu'ils sont conçus et fonctionnent au rythme d'un signal de synchronisation. Ce signal est le signal d'horloge. Il prend souvent la forme d'une onde carrée périodique. En calculant le temps maximum que prend le signal électrique pour se propager dans les différentes branches des circuits du processeur, le concepteur peut sélectionner la période appropriée du signal d'horloge.

Cette période doit être supérieure au temps que prend le signal pour se propager dans le pire des cas. En fixant la période de l'horloge à une valeur bien au-dessus du pire des cas de temps de propagation, il est possible de concevoir entièrement le processeur et la façon dont il déplace les données autour des "fronts" montants ou descendants du signal d'horloge. Ceci a pour avantage de simplifier significativement le processeur tant du point de vue de sa conception que de celui du nombre de ses composants. Par contre, ceci a pour inconvénient le ralentissement du processeur puisque sa vitesse doit s'adapter à celle de son élément le plus lent, même si d'autres parties sont beaucoup plus rapides. Ces limitations sont largement compensées par différentes méthodes d'accroissement du parallélisme des processeurs (Voir ci-dessous).

Les améliorations d'architecture ne peuvent pas, à elles seules, résoudre tous les inconvénients des processeurs globalement synchrones. Par exemple, un signal d'horloge est sujet à des retards comme tous les autres signaux électriques. Les fréquences d'horloge plus élevées que l'on trouve dans les processeurs à la complexité croissante engendrent des difficultés pour conserver le signal d'horloge en phase (synchronisé) à travers toute l'unité centrale de traitement. En conséquence, beaucoup des processeurs d'aujourd'hui nécessitent la fourniture de plusieurs signaux d'horloge identiques de façon à éviter que le retard d'un seul signal ne puisse être la cause d'un dysfonctionnement du processeur. La forte quantité de chaleur qui doit être dissipée par le processeur constitue un autre problème majeur dû à l'accroissement des fréquences d'horloge. Les changements d'état fréquents de l'horloge font commuter un grand nombre de composants, qu'ils soient ou non utilisés à cet instant. En général, les composants qui commutent utilisent plus d'énergie que ceux qui restent dans un état statique. ainsi, plus les fréquences d'horloge augmentent et plus la dissipation de chaleur en fait autant, ce qui fait que les processeurs requièrent des solutions de refroidissement plus efficaces.

La méthode dite de clock gating permet de gérer la commutation involontaire de composants en inhibant le signal d'horloge sur les éléments choisis mais cette pratique est difficile à implémenter et reste réservée aux besoins de circuits à très faible consommation.

Une autre méthode consiste à invalider le signal global d'horloge, la consommation d'énergie et la dissipation thermique sont réduites mais la conception du circuit devient plus complexe. Certaines conceptions ont été réalisés sans signal global d'horloge, comme par exemple les familles de processeurs ARM ou MIPS, d'autres ne présentent que des parties asynchrones comme par exemple l'utilisation d'un ALU asynchrone avec un pipelining superscalaire pour atteindre des gains de performance dans les calculs arithmétiques. Il n'est pas certain qu'un processeur totalement asynchrone puisse délivrer un niveau de performance comparable ou supérieur à un processeur synchrone alors qu'il est évident qu'il sera meilleur dans les opérations mathématiques simples, il sera donc plutôt réservé aux applications embarquées (ordinateurs de poche, consoles de jeux...).

Parallélisme

La description du mode de fonctionnement de base d'un processeur présentée au chapitre précédent présente la forme la plus simple que peut prendre un CPU. Ce type de processeur, appelé subscalaire, exécute une instruction sur un ou deux champs de données à la fois.

Ce processus est inefficace et inhérent aux processeurs subscalaires. Puisqu'une seule instruction n'est exécutée à la fois, tout le processeur attend la fin du traitement de cette instruction avant de s'intéresser à la suivante avec pour conséquence que le processeur reste figé sur les instructions qui nécessitent plus d'un cycle d'horloge pour s'exécuter. L'ajout d'une seconde unité de traitement (voir ci-dessous), ne permet pas d'améliorer notablement les performances, ce n'est plus une unité de traitement qui se trouve figée mais 2, en augmentant encore le nombre de transistors inutilisés. Ce type de conception, dans laquelle les ressources d'exécution du CPU ne traitent qu'une seule instruction à la fois ne peut atteindre que des performances scalaires (une instruction par cycle d'horloge), voire subscalaires (moins d'une instruction par cycle d'horloge).

En tentant d'obtenir des performances scalaires et au-delà, on a abouti à diverses méthodes qui conduisent le CPU a un comportement moins linéaire et plus parallèle. Lorsqu'on parle de parallélisme de processeur, deux termes sont utilisés pour classifier ces techniques de conception :

- Instruction Level Parallelism (ILP) - Parallélisme au niveau instruction ;

- Thread Level Parallelism (TLP) - Parallélisme au niveau thread (groupe d'instructions).

L'ILP cherche à augmenter la vitesse à laquelle les instructions sont exécutées par un CPU (c’est-à-dire augmenter l'utilisation des ressources d'exécution présentes dans le circuit intégré). L'objectif du TLP est d'accroître le nombre de threads que le CPU pourra exécuter simultanément. Chaque méthode diffère de l'autre d'une part, par la façon avec laquelle elle est implémentée et d'autre part, du fait de leur efficacité relative à augmenter les performances des processeurs pour une application.

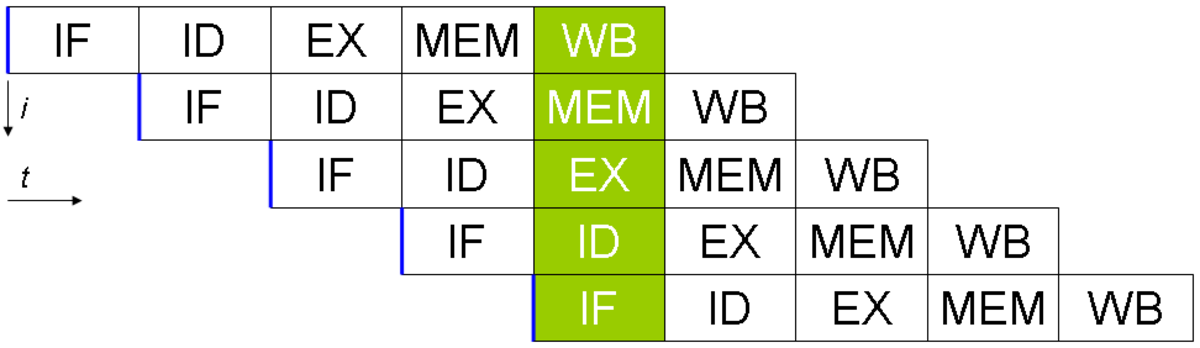

ILP : Pipelining d'instructions et architecture superscalaire

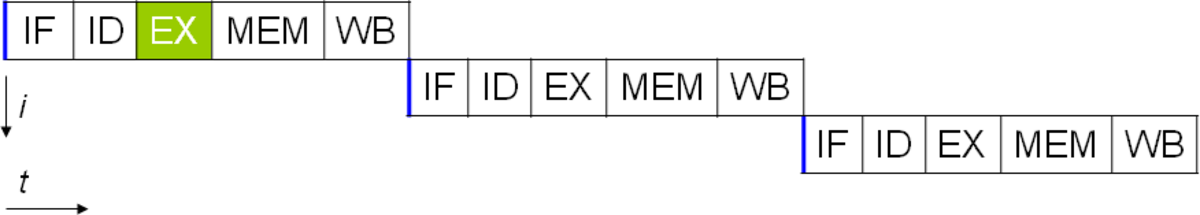

Une des méthodes les plus simples pour accroître le parallélisme consiste à démarrer les premières étapes de recherche (fetch) et décodage (decode) d'une instruction avant la fin d'exécution de l'instruction précédente. C'est la forme la plus simple de la technique de pipelining, elle est utilisée dans la plupart des processeurs modernes non spécialisés. Le pipelining permet d'exécuter plus d'une instruction à la fois en décomposant le chemin d'exécution en différentes étapes. Ce découpage peut être comparé à une chaîne d'assemblage.

Le pipelining peut créer des conflits de dépendance de données, lorsque le résultat de l'opération précédente est nécessaire à l'exécution de l'opération suivante. Pour résoudre ce problème, un soin particulier doit être apporté pour vérifier ce type de situation et retarder, le cas échéant, une partie du pipeline d'instruction. Naturellement, les compléments de circuits à apporter pour cela ajoutent à la complexité des processeurs parallèles. Un processeur parallèle peut devenir presque scalaire, ralenti uniquement par les attentes du pipeline (une instruction prend moins d'un cycle d'horloge par étape).

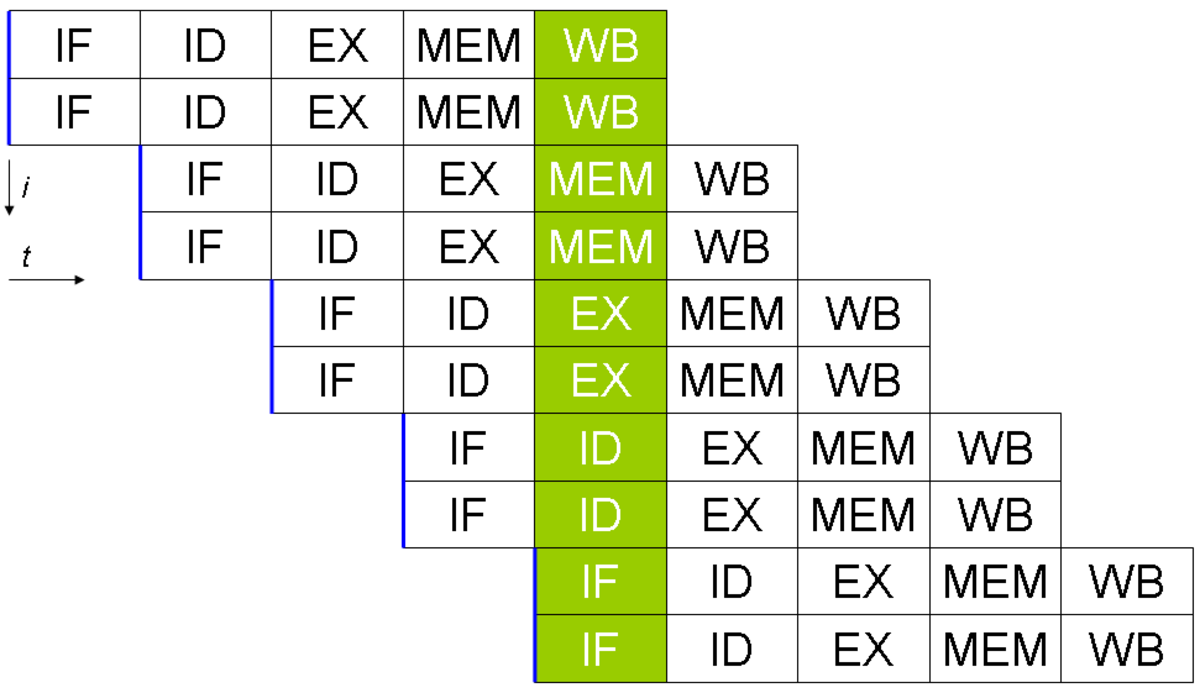

Les développements suivants du pipelining ont conduit au développement d'une méthode qui diminue encore plus les temps d'attente des composants du processeur. Les conceptions dites superscalaires comportent un pipeline à instruction longue et plusieurs unités d'exécution identiques. Dans un pipeline superscalaire, plusieurs instructions sont lues et transmises à un répartisseur qui décide si les instructions seront exécutées en parallèle (simultanément) ou non. Le cas échéant, les instructions sont réparties sur les unités d'exécution disponibles. En général, plus un processeur superscalaire est capable d'exécuter d'instructions en parallèle et plus le nombre d'instructions exécutées dans un cycle sera élevé.

La plupart des difficultés rencontrées dans la conception des architectures de processeurs superscalaires résident dans la mise au point du répartisseur. Le répartisseur doit être disponible rapidement et être capable de déterminer sans erreur si les instructions peuvent être exécutées en parallèle, il doit alors les distribuer de façon à charger les unités d'exécution autant qu'il est possible. Pour cela, le pipeline d'instructions doit être rempli aussi souvent que possible, créant le besoin d'une quantité importante de mémoire cache. Les techniques de traitement aléatoire comme la prédiction de branchement, l'exécution spéculative et la résolution des dépendances aux données deviennent cruciales pour maintenir un haut niveau de performance. En tentant de prédire quel branchement (ou chemin) une instruction conditionnelle prendra, le processeur peut minimiser le nombre de fois que tout le pipeline doit attendre jusqu'à la fin d'exécution de l'instruction conditionnelle. L'exécution spéculative améliore les performances modestes en exécutant des portions de code qui seront, ou ne seront pas, nécessaires à la suite d'une instruction conditionnelle. La résolution de la dépendance aux données est obtenue en réorganisant l'ordre dans lequel les instructions sont exécutées en optimisant la disponibilité des données.

Lorsque seule une partie de processeur est superscalaire, la partie qui ne l'est pas rencontre des problèmes de performance dus aux temps d'attente d'ordonnancement. Le Pentium original (P5) disposait de 2 ALU superscalaires qui pouvaient chacune accepter une instruction par cycle. Ensuite le P5 est devenu superscalaire pour les calculs sur les nombres entiers mais pas sur les nombres à virgule flottante. Les successeurs des architectures Pentium d'Intel, les P6, ont été dotés de capacités superscalaires pour les calculs sur les nombres à virgule flottante améliorant par là leurs performances en calcul flottant.

Les conceptions de pipelining simple et superscalaires augmentent le parallélisme (ILP) des CPU en permettant à un processeur unique d'exécuter des instructions à un rythme de plus d'une instruction par cycle. La plupart des processeurs d'aujourd'hui ont au moins une partie superscalaires. Au cours des dernières années, certaines évolutions dans la conception des processeurs à fort parallélisme ne se trouvent plus dans les circuits du processeur mais ont été placées dans le logiciel ou dans son interface avec le logiciel (ISA). La stratégie des instructions très longues (very long instruction word) conduit à implémenter certains parallélismes directement dans le logiciel, cela réduit la participation du processeur au gain de performance mais en réduit la complexité.

TLP : Exécution simultanée de programmes

Une autre stratégie communément employée pour augmenter le parallélisme des processeurs consiste à introduire la capacité d'exécuter plusieurs programmes (threads) simultanément. De manière générale, les processeurs multi-threads ont été utilisés depuis plus longtemps que les processeurs à architecture pipeline. Bon nombre des conceptions pionnières, réalisées par la société Cray Research, datant de la fin des années 1970 et des années 1980, mettaient en œuvre principalement la méthode TLP, dégageant alors de très grandes capacités de calcul (pour l'époque). En fait, le multithreading était connu dès les années 1950 (Réf : Smotherman 2005).

Dans le cas des processeurs simples, les 2 méthodologies principales employées pour développer des TLP sont le multiprocessing au niveau des circuits (Chip-level multiprocessing - CMP) et le multithreading simultané (Simultaneous multithreading - SMT). À un plus haut niveau, il est d'usage de réaliser des ordinateurs avec plusieurs processeurs totalement indépendants dans des organisations de type symétrique (symetric multiprocessing - SMP) ou à accès mémoire non uniforme (non uniform memory access - NUMA). Alors que ces techniques diffèrent par les moyens qu'elles mettent en œuvre, elles visent toutes le même but : augmenter le nombre de threads qu'un processeur peut exécuter en parallèle.

Les méthodes de parallélisme CMP et SMP sont assez semblables, elles demandent plus d'effort de conception que l'utilisation de 2 ou 3 processeurs totalement indépendants. Dans le cas du CMP, plusieurs cœurs (core, en anglais) de processeurs sont intégrés dans le même boîtier, parfois même dans le même circuit intégré. Les SMP, eux, utilisent plusieurs boîtiers indépendants. NUMA est comparable au CMP mais met en œuvre un modèle d'accès mémoire non uniforme (les temps d'accès sont différents suivant que la mémoire est locale ou non locale à un processeur donné). Cette caractéristique est fondamentale dans les ordinateurs à plusieurs processeurs car pour les modèles SMP à mémoire partagée, les temps d'accès à la mémoire sont rapidement dégradés en cas d'accès simultané par plusieurs processeurs. À ce titre, NUMA est considéré comme un modèle plus évolutif en nombre de processeurs.

SMT diffère des autres améliorations de TLP puisqu'il vise à dupliquer aussi peu de portions de CPU que possible. La mise en œuvre d'une stratégie de type TLP ressemble à une architecture superscalaire et se trouve souvent utilisée dans les microprocesseurs superscalaires (comme les POWER5 d'IBM). Plutôt que de dupliquer un CPU complet, la conception SMT ne duplique que les parties nécessaires pour la recherche (fetch), le décodage, (decode) et la répartition des instructions (dispatch) ainsi que les registres non spécialisés. Ceci permet a un processeur SMT de maintenir ses unités d'exécution occupées plus souvent, en leur fournissant des instructions en provenance de 2 programmes différents. Comme on vient de la voir, le SMT est proche de l'architecture ILP superscalaire mais, plutôt que d'exécuter simultanément plusieurs instructions en provenance de 2 programmes différents, elle permet d'exécuter simultanément plusieurs instructions en provenance du même programme.