AMD K10 - Définition

La liste des auteurs de cet article est disponible ici.

Introduction

La microarchitecture K10, la neuvième d'AMD, succède à la microarchitecture K8.

Elle est introduite sur le Phenom. Par rapport à K8, les flottants sont désormais traités sur 128bits, et la bande passante interne augmente.

Nomenclature

AMD abandonne le P-rating (xx00+) pour une nouvelle numérotation en 2 lettres plus 4 chiffres :

- 1ère lettre : gamme

- 2ème lettre : dissipation (TDP)

- 1er chiffre : famille/architecture : 7 = Phenom 4 cœurs ; 6 = Phenom bi cœurs ; 2 = Athlon X2 ; 1 = Athlon mono cœur et Sempron

- 2ème chiffre et 3ème chiffre : puissance en fréquence

- 4ème chiffre : fonctionnalités éventuelles

Technologies et caractéristiques

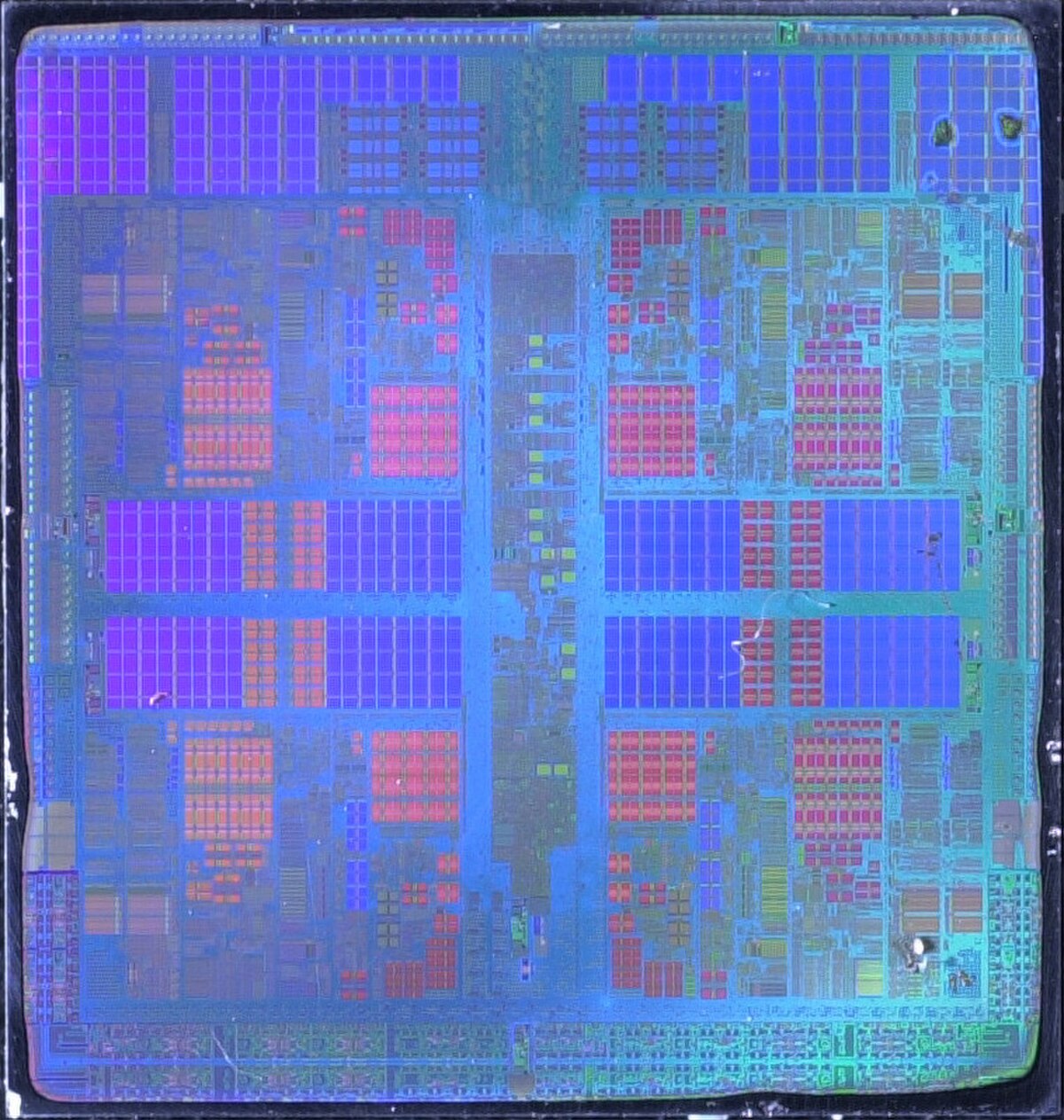

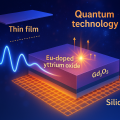

Gravure

Les premiers microprocesseurs de la génération K10 seront exclusivement gravés grâce à la technologie de gravure en 65 nm d'AMD en partenariat avec IBM qui utilise des wafers SOI (Silicium sur isolant) 300 mm UNIBOND™ du fabricant français Soitec qui entretient un partenariat privilégié avec AMD. Le partenariat avec IBM permet également à AMD d'utiliser la technologie SiGe d'IBM (ajout de germanium en plus de silicium en vue de rendre les transistors plus performants). Ces microprocesseurs seront sûrement fabriqués dans l'usine Fab 36 d'AMD à Dresde en Allemagne qui fabrique déjà les Athlon 64 en 65 nm. L'usine pourra produire normalement aux alentours de 100 millions de processeurs par an dès 2008 (pour 20 000 wafers) ce qui coïncide avec l'arrivée de l'architecture K10. AMD utilise pour sa gravure en 65 nm ses technologies Continuous Transistor Improvement (CTI) ou amélioration continue de transistor et Shared Transistor Technology (STT) ou partage technologique des transistors ainsi que la technologie Dual Stress Liner (DSL).

Il existera peut-être par la suite des processeurs K10 gravés en 45 voire en 32 nm (Deneb FX, Deneb, Propus, Regor et Sargas), puisqu'AMD compte produire des processeurs grâce à la technologie de lithographie par immersion dès 2008.

Mémoire

Les processeurs de la famille K10 tout comme leurs prédécesseurs K8 possèderont leur contrôleur mémoire intégré contrairement aux processeurs Intel qui laissent cette charge au chipset. Cette caractéristique a été en partie responsable du succès des Athlon 64 en réduisant considérablement les latences pour l'accès à la mémoire RAM lorsque la norme était la DDR-SDRAM première du nom. En effet avec ce type de barrettes, les latences de la RAM étaient de 2-2-2-5 pour les meilleures DDR400. Mais lors de l'introduction de la DDR2, l'atout de l'Athlon 64 s'est atténué car les latences ont explosé et l'augmentation de fréquence n'a pu que compenser cette chute de performance. Ainsi les Athlon 64 sur socket AM2 sont juste aussi performants que les Athlon 64 sur socket 939. Les latences mémoires ayant sérieusement diminué, la DDRII ne pose plus de problème. Les K10 seront faits pour supporter de la DDR2 1066MHz en standard. Les serveurs exploiteront la DDR2 800 dans un premier temps.

Les prochaines révisions de cœur de la famille K10 (Deneb FX, Deneb, Propus, Regor et Sargas) prévues pour l'année 2008 voire 2009 seront elles, tournées vers la mémoire DDR3 et le 45 nm qui n'est pas encore sur le marché. Ils seront équipés de 4 ou 6 Mio de cache L3.

Sockets

AMD a fait le choix d'une certaine continuité lors de ce passage au K10. Il n'y aura donc pas comme lors du passage de l'architecture K7 à K8 un changement radical de socket (alors socket A vers socket 754 puis 939 et AM2). AMD a donc nommé le socket de son nouveau processeur AM2+ pour marquer la proximité avec le socket AM2. Le socket AM2+ accueillera donc tous les processeurs K10 à l'exception des processeurs socket 1207 incompatibles. Il s'agit d'un socket de 940 broches. Les différences entre le socket AM2 utilisé actuellement pour les K8 et le socket AM2+ seront la gestion de l'hypertransport 3.0 par ce dernier et la gestion avancée de l'énergie puisque chaque cœur disposera d'une tension propre. Sur socket AM2, les processeurs pourront tout de même varier leur fréquences indépendamment mais pas leur tension. Il y a rétro compatibilité et on pourra profiter de l'architecture K10 sur une carte mère AM2.

Les chipsets pour AM2+ déjà annoncés sont le Nvidia Nforce 7 nom de code MCP72, le VIA KT960 et KM960 mais aussi les chipsets d'ATI (maintenant propriété d'AMD) RD790+, RD780, RS780, RX780, RS740 et RX740.

Les K10 socket AM3 auront probablement deux contrôleurs mémoire, un DDR2 et un DDR3 ainsi ils fonctionneront parfaitement avec une carte mère AM2+. Cependant cette information est à mettre entre pincettes, AMD pourrait très bien changer d'avis car le coût en transistors de deux contrôleurs mémoire pourrait être élevé.

Un K10 AM2+ ne sera pas compatible AM3.

Spécifications

Les caractéristiques complètes des K10 sont celles du premier cœur K10, à savoir le Barcelona. Les versions desktop seront sans doute différentes puisque le Barcelona est fait pour le marché serveur aux demandes particulières.

- Généralités.

- Deux contrôleurs mémoire DDR2 intégrés (Le contrôleur mémoire 128bits des K8 est séparé en deux contrôleurs 64bits pour le K10. Passage prévu à un contrôleur mémoire DDR3).

- Fréquence de fonctionnement entre 1900 et 2 600 MHz (Les versions desktop devraient atteindre les 2 800 MHz).

- 16 niveaux de pipeline.

- Gestion de l'hypertransport 3.0 pour des bus au-delà de 3 GHz (sur socket AM2+, sur socket AM2 la fonction ne sera pas exploitée).

- cache.

- 64 Kio de cache L1 données par cœur (taille identique à celle des K8)

- 64 Kio de cache L1 instructions par cœur (taille identique à celle des K8)

- 512 Kio de cache L2 par cœur (taille identique aux derniers K8. Les Kentsfield offrent 2x4 Mio de cache L2 et le futur Penryn jusqu'à 2×6 Mio).

- 2 Mio de cache L3 partagé.

- Extension possible jusqu'à 8 Mio, 4 à 6 Mio avec le passage au 45 nm: cœur Shangai.

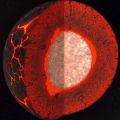

- Le die.

- 1er quadri-cœur dit « natif » produit en masse (Il ne s'agit pas de la juxtaposition de deux circuits bi-cœur comme pour les Core 2 quad Intel.

- Composé de 11 couches de gravure (Contre 9 pour les K8 et 8 pour les core 2 duo. Cela rend le procédé de fabrication un peu plus complexe mais ne change rien pour l'utilisateur. Intel utilisait aussi ce type de procédé avec autant de couches il y a quelques années).

- 463 millions de transistors (Face au 582 millions du Kentsfield mais gravé sur deux die. Ceci s'explique par le fait que le Kentsfield embarque 8,25 Mio de cache alors que le Barcelona se limite à 5,5 Mio).

- 60 millions de transistors non-caches (soit 30%) en plus par rapport au K8.

- améliorations du pipeline et nouvelles Instructions.

- Le SSE 128,

- Gestion d'instruction d'une longueur de 128bits (Contre 64bits pour le K8).

- Gestion parallèle de 32 octets par cycle (Soit le double d'avec le K8. Amélioration qui pourrait bénéficier à d'autres types d'opérations comme par exemple sur les entiers).

- Deux chargements d'instructions par cycle depuis le cache L1 (Nombre stable par rapport au K8 mais donc deux fois plus de données chargées par cycle du fait du passage d'instructions 2*64 à 2*128bits).

- Interface élargie entre le cache L2 et le contrôleur mémoire à 128bits (Pour la cohérence de l'architecture, c'est à dire éviter un goulot d'étranglement).

- Introduction des instructions SSE4A.

- Extensions des instructions SSE : EXTRQ/INSERTQ et MOVNTSD/MOVNTSS.

- Apparition des instructions LZCNT et POPCNT utilisées en cryptographie.

- Diminution de la latence sur les divisions d'entiers (ALU) (Les conséquences pratiques devraient être minimes)

- 4 FPU (Floating Point Unit, unités de calcul à virgule flottante) (au lieu de 2 pour le K8. AMD parle d'une amélioration théorique de +300% des performances face au bi-cœur K8 (deux fois plus de cœurs avec deux fois plus de FPU, donc performances quadruplées), mais finalement en pratique l'amélioration serait de l'ordre de 50% face à la concurrence).

- Fastpath.

- Les microinstructions CALL and RET-Imm sont maintenant des instructions qui utilisent Fastpath (elles ne sont plus microcodées).

- Les déplacements entre registres des entiers et registres SSE des instructions MOVs utilisent aussi le Fastpath.

- Le SSE 128,

- Sous-système mémoire, cache et prefetch.

- Diminution de la latence au niveau du cache.

- Meilleure gestion de données Out-Of-Order.

- Prédictions,

- Apparition d'un prédicateur de branchement indirect: 512-entry indirect predictor (Intel avait ajouté ce type de prédicateur sur ses PIV Prescott qui pâtissaient de leur long pipeline et toute erreur de branchement représentait une perte de temps considérable).

- L'espace dédié à la "pile de retour" (return stack) est multiplié par deux.

- La prédiction directe est aussi améliorée par l'augmentation des données "historiques" (Possibilité offerte par la taille gagnée avec le passage au 65 nm alors que l'architecture K8 se contentait au départ du 130 nm).

- Sideband Stack Optimizer équivalent au Dedicated Stack Manager d'Intel.

- TLB (Translation Lookaside Buffer)

- Extension.

- Adressage physique 48bits permettant la gestion de mémoire jusqu'à 256 Tio

- Prefetch:

- 2 prefetch par cœur, un pour les données et un pour les instructions (AMD conserve le nombre de prefetch du K8. À noter que les C2D d'Intel en possèdent trois par cœur).

- Le prefetch charge dans le cache L1 (Le prefetch chargeait dans le cache L2 chez les K8).

- Apparition d'un prefetch de RAM utilisant son propre cache.

- Virtualisation.

- Virtualisation de la mémoire Nested Paging

- Énergie.

- Le voltage du northbridge est maintenant indépendant et s'échelonne de 0.8V à 1.4V.

- Apparition du DICE ou Dynamic Independent Core Engagement ou gestion matérielle du PowerNow! permettant la gestion indépendante de la fréquence de chaque cœur.

- TDP compris entre 95W et 120W (TDP entre 45W et 89W pour les Phenom, TDP inconnu pour les Phenom FX)

- Registres

- ajouts de 8 registres supplémentaire pour le 64bits.

Performances

Lors d'une démonstration le 30 novembre 2006, AMD annonce et montre à la presse que le Barcelona sera globalement 40% plus performant qu'un Xeon 5355 (quad-core à 2,66 GHz). Dernièrement AMD affirme que son processeur devrait devancer les performances des Xeon quadri-cœurs de 50% sur les calculs en virgule flottante et de 20% sur des calculs liés à des nombres entiers. Cela dit, il est bon de préciser qu’une telle comparaison ne peut pas encore être vérifiée et que cette comparaison s’applique pour des fréquences égales entre le processeur d’architecture K10 d’AMD et le Xeon d’Intel. De plus il ne s'agit là que de tests théoriques.

Début mai 2007, AMD a fait une nouvelle démonstration plutôt impressionnante de ses futurs K10. C'est au CTO Technology Summit à Monterey, en Californie qu'AMD a dévoilé une machine disposant de deux processeurs K10 quadri-cœurs. La machine de 8 cœurs a été capable d'encoder à la volée, c'est-à-dire en temps réel, une vidéo 720p (1280 × 720) et une 1024p.